| 失效链接处理 |

|

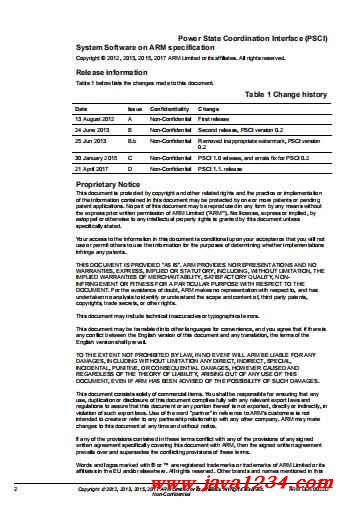

Power_State_Coordination_Interface_PDD PDF 下载

本站整理下载:

提取码:nnw7

相关截图:

主要内容:

Introduction

This document defines a standard interface for power management that can

be used by OS vendors for supervisory software working at different levels

of privilege on an ARM device. Rich operating systems like Linux and

Windows, hypervisors, secure firmware, and Trusted OS implementations

must interoperate when power is being managed. The aim of this standard

is to ease the integration between supervisory software from different

vendors working at different privilege levels.

The interface is aimed at the generalization of code in the following power

management scenarios:

Core idle management.

Dynamic addition and removal of cores, and secondary core boot.

System shutdown and reset.

The interface does not cover Dynamic Voltage and Frequency Scaling

(DVFS) or device power management (for example, management of

peripherals such as GPUs).

The interface is designed so that it can work in conjunction with hardware

discovery technologies such as Advanced Configuration and Power

Interface (ACPI) and Flattened Device Tree (FDT). It is not a replacement

for ACPI or FDT.

This document describes PSCI versions 1.1, 1.0, and 0.2. For PSCI 0.2, the

document provides an errata fix update. The PSCI 0.2 erratum applies to a

single function and is described in section 5.1.7.

The document is arranged into the following sections:

Section 1 provides this introduction and references.

Section 2-4 provide background materials, including:

Intended uses of PSCI.

Background definitions of power state terms. Methods by which PSCI requests are made.

ARM architecture background.

Section 5 provides the main description of the PSCI functions.

Section 6 provides additional implementation details.

Sections 7 and 8 provide a revision history of the PSCI

specification and a glossary.

Readers already familiar with PSCI can skip straight to section 5.

1.1 Additional reading

This section lists publications by ARM and by third parties.

Introduction

Copyright 2012, 2013, 2015, 2017 ARM Limited or its affiliates. All rights reserved.

Non-Confidential

See Infocenter, http://infocenter.arm.com, and http://developer.arm.com for

access to ARM documentation.

1.1.1 ARM publications

The following documents contain information that is relevant to this

document:

[1] ARM Architecture Reference Manual ARMv7-A and ARMv7-R edition

(ARM DDI 0406).

[2] Embedded Trace Macrocell Architecture Specification (ARM IHI 0014).

[3] Program Flow Trace Architecture Specification (ARM IHI 0035).

[4] SMC Calling Conventions (ARM DEN 0028).

[5] ARM Architecture Reference Manual ARMv8, for ARMv8-A

architecture profile (ARM DDI 0487).

[6] Advanced Configuration and Power Interface Specification. See http://www.uefi.org/sites/default/files/resources/ACPI_6_1.pdf.

[7] PSCI device tree definition.

https://www.kernel.org/doc/Documentation/devicetree/bindings/arm/psci

.txt.

[8] ARM Trusted Firmware.

See https://github.com/ARM-software/arm-trusted-firmware

[9] Power Control System Architecture Specification (ARM DEN 0050).

1.1 Feedback

ARM welcomes feedback on its documentation.

1.1.1 Feedback on this manual

If you have comments on the content of this manual, send an e-mail to

errata@arm.com. Provide:

The title.

The number, ARM DEN 0022D.

The page numbers to which your comments apply.

A concise explanation of your comments.

ARM also welcomes general suggestions for additions and improvements.

Background

8 Copyright 2012, 2013, 2015, 2017 ARM Limited or its affiliates. All rights reserved. ARM DEN 0022D

Non-Confidential

2 Background

Power management aware operating systems dynamically change the

power states of cores, balancing the available compute capacity to match

the current workload, while striving to use the minimum amount of power.

Some of these techniques dynamically switch cores on and off or place

them in quiescent states, where they no longer perform computation. This

means they consume very little power. The main examples of these

techniques are:

Idle Management: When the kernel in an OS has no threads to schedule

on a core, it places that core into a clock-gated, retention, or even

fully power-gated state. However, the core remains available to the

OS.

Hotplug: Cores are physically switched off when compute demand is low,

and then brought back online when it increases. The OS migrates all

interrupts and threads away from the cores that are taken offline, and

rebalances the load when they are brought back online.

Although it would be simpler to consider the software of an embedded

system to be provided by a single vendor, in most situations this is not the

case, even when the end device is delivered with fixed functionality. The

ARM architecture defines a set of Exception levels [5] that support the

required partitioning of the software stack used on a device. Table 2 shows

this partitioning and indicates the typical vendor of each level of the stack:

Table 2 Typical partitioning of software on a system that complies with the ARM

|

苏公网安备 32061202001004号

苏公网安备 32061202001004号